## TRABAJO PRÁCTICO Nº 7 CONVERSION ANALOGICA-DIGITAL

## 7.1 Conversor digital-analógico

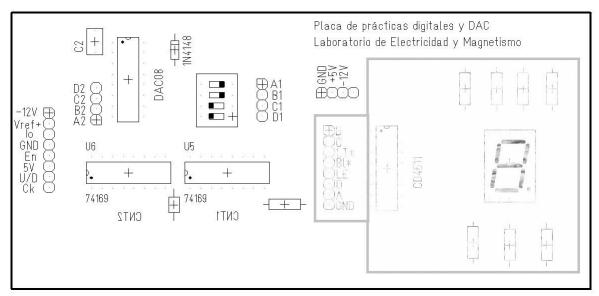

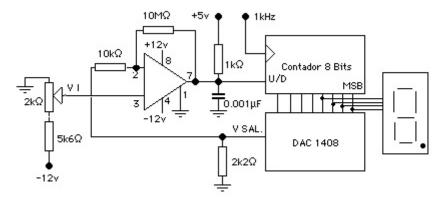

A los efectos de simplificar el trabajo se ha armado una parte del circuito a utilizar en una plaqueta. Enchúfela en un sector del demostrador dejando espacio para agregar más componentes. La Figura 7.1 muestra un esquema de la plaqueta. Los terminales del Conector corresponden, de arriba hacia abajo, a:  $\mathbf{1}$  -12V (e),  $\mathbf{2}$  Vref (e),  $\mathbf{3}$  Io (s),  $\mathbf{4}$  Gnd (e),  $\mathbf{5}$  E(e),  $\mathbf{6}$  +5V (e),  $\mathbf{7}$  U/D (e),  $\mathbf{8}$  clock (e), donde (e) indica entrada y (s) salida. Si ya utilizó el conector ubicado en el centro de la plaqueta para alimentar Gnd, +5V y -12V, entonces no hace falta que conecte los terminales de alimentación (1, 4 y 6). Conecte una resistencia de  $2k2\Omega$  entre Io y tierra para tener Vout y una de  $5k6\Omega$  entre Vref y +12V. La zona grisada de la Figura 7.1 corresponde al Diplay de 7 segmentos con su decodificador BCD.

Fig. 7.1.a Plaqueta con contadores y DAC

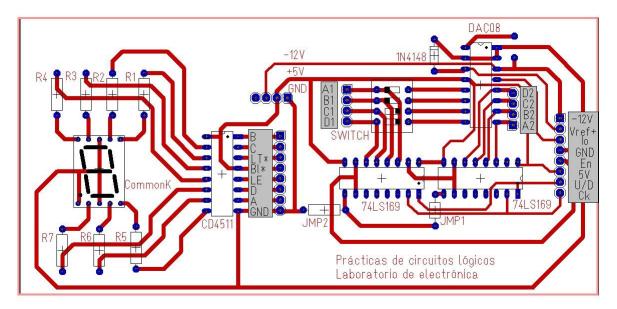

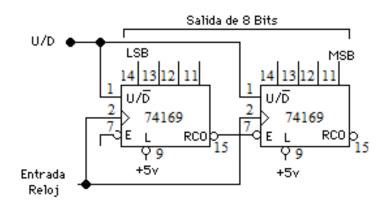

Comience probando el contador sincrónico de 8 bits ascendente / descendente utilizando los dos integrados 74169, tal como se muestra en la figura 7.2. Las salidas de los contadores se pueden medir en los dos zócalos de 4 patas del centro de la plaqueta (A1 – D1 los menos significativos y A2 – D2 los más significativos). (Puede ver como se conectan los componentes en la F1gura 7.1.b. Tenga en cuenta que es una vista posterior, por lo que las patas de los integrados se cuentan en el sentido horario.

Fig. 7.1.b Plaqueta con contadores y DAC – Vista Posterior con conexiones

Verifique la secuencia de conteo en los modos ascendente (U/D = alto) y descendente (U/D = bajo). Compruebe la función que cumple la pata de habilitación (E) (En este caso la pata de carga (LOAD) ha sido conectada a 5V. ¿Por qué?). Explique cómo funciona esta forma de acoplar contadores.

Fig. 7.2 Contador sincrónico de 8 bits

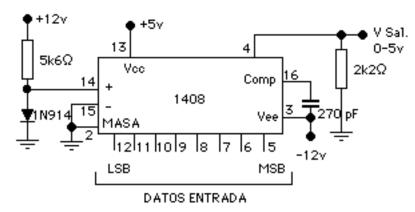

A continuación utilice la salida de los contadores para comandar el conversor DAC0800-1408, como se indica en la figura 7.3. Una los terminales del zócalo de los cuatro bits menos significativos (los cuatro mas significativos están unidos en la plaqueta) usando el micro switch. Aplique al conversor una señal de reloj de 1kHz y observe la salida del DAC con un osciloscopio.

Fig. 7.3 Conversor Digital-Analógico

Invierta la dirección de conteo y explique la diferencia que se observa a la salida del DAC. Explique el rol que juega la resistencia de  $2k2\Omega$  y la de  $5k6\Omega$ . Para ello reemplace la resistencia de  $2k2\Omega$  por una de  $1k8\Omega$  e indique las diferencias observadas. Haga lo mismo con la de  $5k6\Omega$  reemplazándola por una de  $6k8\Omega$ . ¿Qué ocurre si, usando el micro switch, desconecta las salidas del contador con bits menos significativos? Observe a la salida del DAC y trate de relacionar la cantidad de escalones de la "escalera" de salida con la cantidad de bits binarios de entrada.

## 7.2 Conversor analógico-digital por localización (traking converter)

Construya un conversor analógico-digital simplemente cerrando el lazo entre la salida de **tensión** del DAC y la entrada U/D de los contadores 74169 con un comparador del tipo "Schmitt" usando un 311 (ver 2.10) como lo indica la figura 7.4.

Fig. 7.4 Conversor Analógico Digital

El potenciómetro de  $2k\Omega$  simula una entrada analógica VI. Explique detalladamente como funciona este circuito. ¿Por qué la tensión del potenciómetro se hace variar entre 0V

y -3V? ¿Qué pasaría si se intercambian las entradas 2 y 3?

Las salidas de los contadores es la salida del Conversor Analógico Digital (DAC). Esta salida es la representación DIGITAL de la tensión analógica del potenciómetro. Lleve a un display los cuatro bits (use el display de la práctica 6) más significativos de los contadores, mueva lentamente el potenciómetro de  $2k\Omega$  y explique lo que observa. ¿Por qué en los extremos del potenciómetro la salida varía constantemente? Pruebe reemplazando la referencia de tensión VI, hecha con el potenciómetro de  $2k\Omega$  y la resistencia de  $5k6\Omega$ , por un oscilador. Ajuste la amplitud y el offset. ¿Qué frecuencia debe tener el oscilador para que el conversor funcione correctamente? ¿Pruebe con una señal senoidal, triangular y cuadrada? ¿Cuál es la variación máxima de la señal analógica por unidad de tiempo que puede convertirse? Compare este valor con la estimación teórica. ¿Cómo se puede mejorar dicha limitación?

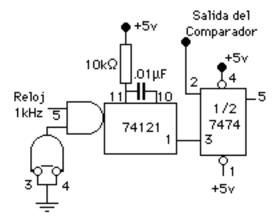

Mire la tensión de salida del 1408 que debería estar siempre cambiando entre dos niveles adyacentes de la escalera. Fíjese si observa saltos más largos, que solo ocurren cuando varía la señal de entrada, y no cuando el DAC se está moviendo a lo largo de la rampa hasta su nuevo estado. El 74169, a diferencia por ejemplo del 74191, tiene un circuito interno que hace que los cambios en las entradas de habilitación y modo ascendente y descendente estén sincronizados con el reloj. Si de todas formas observa saltos, estos son causados por un error en la secuencia del 74169 que ocurre cuando la entrada E y U/D mientras el reloj está en el nivel bajo. Para verificar que este es el origen del problema, dibuje un diagrama de tiempos para el reloj y para la salida del comparador. Una solución para este problema es la propuesta en la figura 7.5. Explique cómo funciona.

Fig. 7.5 Solución para el problema del 74191